Field Programmable Pin-Constrained DMFB

Field-Programmable Pin-Constrained DMFB

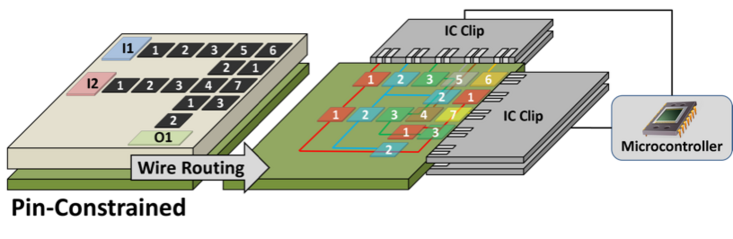

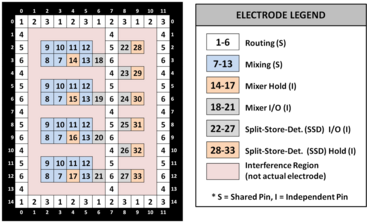

The Field-Programmable Pin-Constrained (FPPC) DMFB, shown below, is a pre-computed pin assignment scheme that is general-purpose and programmable, rather than being application-specific. In many respects, it can be viewed as a pin-constrained version of a virtual topology, in which pin-constrained Work Modules are dedicated for mixing, and separately for splitting, storage, and detection (SSD), with a separate interconnection network consisting of horizontal and vertical three-phase transport buses.

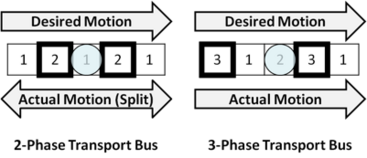

The image below depicts the rationale for a three-phase (rather than two-phase) transport bus.

The FPPC requires dedicated scheduling, placement, and routing algorithms, which are included in the framework. These algorithms are not compatible with any other pin assignment, including direct addressing.

The FPPC and its supporting algorithms were introduced in the following paper:

D. Grissom and P. Brisk

A Field-programmable Pin-constrained Digital Microfluidic Biochip

50th Design Automation Conference (DAC)

Austin, TX, USA, June 2-6, 2013, article #46

Paper Slides

Reduced-cost FPPC Design

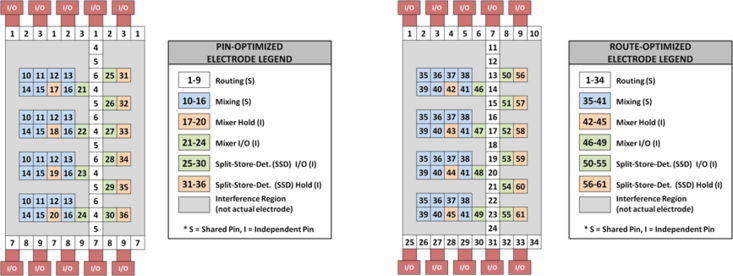

The FPPC, as shown above, achieves general-purpose programmability, but at a fairly high cost in terms of PCB layers. In response, we redesigned the FPPC to reduce the number of PCB layers required for the escape router. Two variants of the reduced-cost FPPC are shown below. :

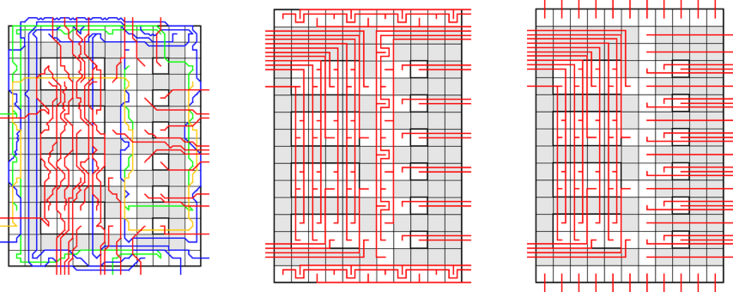

Left: The vertical transport busses from the left and right sides of the FPPC have been removed; this limits the capability to transport droplets concurrently, but simplifies escape routing. Additionally, an extra row has been added just beneath the topmost transport bus to facilitate the necessary wires for single-PCB-layer escape routing.

Right: To enhance the ability to route droplets concurrently, the horizontal and vertical transport busses are replaced with direct addressing. This improves routing performance, but increases the number of control pins required, and therefore increases the total cost of the chip.

The escape routing solutions for the original and reduced-cost FPPCs are shown below. The original requires four PCB routing layers (left), while both reduced-cost variants can be escape-routed using a single layer (center, right).

The reduced-cost FPPC was introduced in the following paper:

D. Grissom, J. McDaniel, and P. Brisk

A Low-cost Field-Programmable Pin-Constrained Digital Microfluidic Biochip

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)

33(11):1657-1670, November, 2014

Paper

Contact

Please direct any questions, comments, or other inquiries to the following e-mail address: microfluidics@cs.ucr.edu

Acknowledgment

This material is based upon work supported by the National Science Foundation under Grant Numbers 1035603, 1536026, and 1545097. Any opinions, findings, and conclusions or recommendations expressed in this material are those of the author(s) and do not necessarily reflect the views of the National Science Foundation.